JUNE 11/2010 www.edn.com

Tales from the Cube: An old PAL saves the day Pg 58

The crash of 2:45 pm, network theory, and the future of SOC design Pg 9

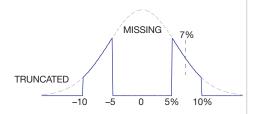

> Signal Integrity: 7% solution Pg 22

Design Ideas Pg 47

VOICE OF THE ENGINEER

# United for a better world

NEC Electronics Corporation and Renesas Technology Corp. have combined their businesses to launch **Renesas Electronics Corporation.**

Renesas Electronics has integrated the microcontroller, power and analog semiconductors, as well as the advanced technologies and strong experience of both companies, to provide system solutions for the global market. As the #1 supplier of microcontrollers in the world\*, the new Renesas Electronics has a corporate vision to harness the power of semiconductors to realize intelligent devices that can enable a sustainable planet and improve the lives of both current and future generations. Together we can realize a society where life can be enjoyed in harmony with the planet.

Source: Gartner, "Semiconductor Applications Worldwide Annual Market Share: Database" 25 March 2010 This is the 2009 ranking based on revenue.

www.renesas.com

Renesas Electronics

RENESAS

# COUNTLESS ON CONTROL OF ORDER OF THE COURT O

440+ Suppliers

#1 Breadth of Product Line

**#1 Availability of Product #1 Overall Performance**

Source: **EETImes** Distribution Study, August 2009

The industry's broadest product selection available for immediate delivery

www.digikey.com 1.800.344.4539

\*Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2010 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

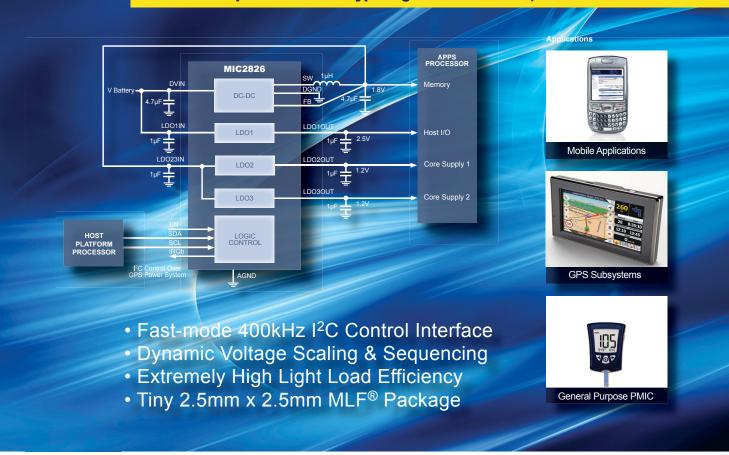

# Advanced Portable System Power Management ICs

Quad Output PMIC with HyperLight Load™ DC/DC, 3 LDOs and I<sup>2</sup>C Control

**Today's** advanced portable electronics require highly integrated power system solutions for complex system power, small size, and long battery life. Micrel provides complete system power solutions, such as the MIC2826, to meet these needs.

The MIC2826 integrates a single 500mA HyperLight Load™ synchronous buck (step-down) regulator with three Low Dropout Regulators in a tiny 2.5mm x 2.5mm Thin MLF® package. The MIC2826 also features a standard 400kHz Fast-mode I²C interface that provides Dynamic Voltage Scaling (DVS), programmable power sequencing, and individual output control, making it the perfect integrated power system solution.

For more information, contact your local Micrel sales representative or visit Micrel at: www.micrel.com/ad/mic2826.

Ideal for use in:

- Application Processors

- GPS Subsystems

- ◆ Mobile Phones/PDAs

- Portable Media Players

- General Purpose PMIC

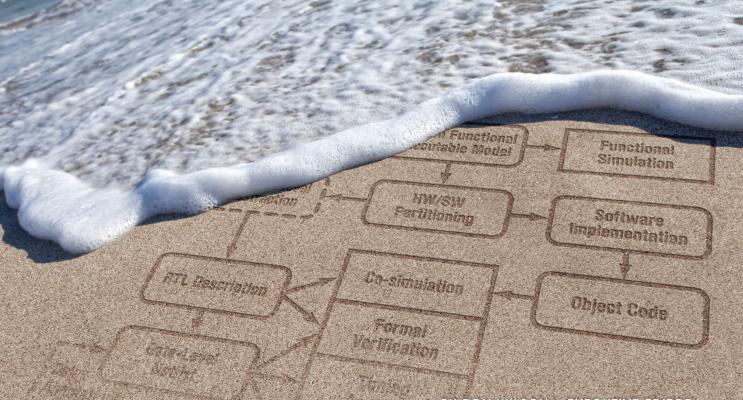

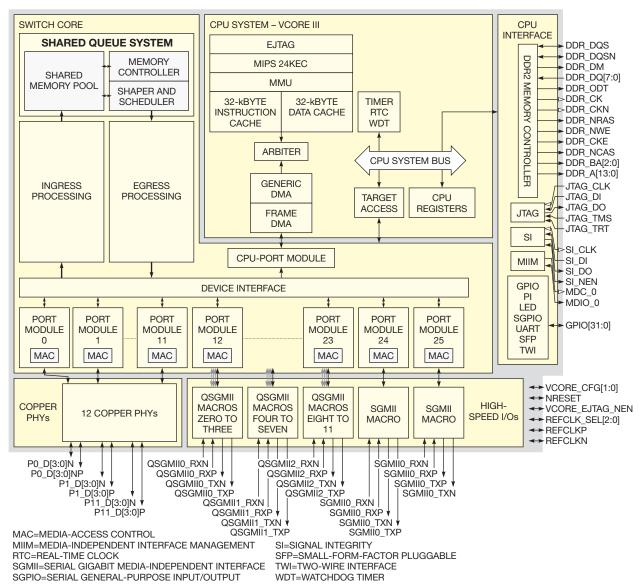

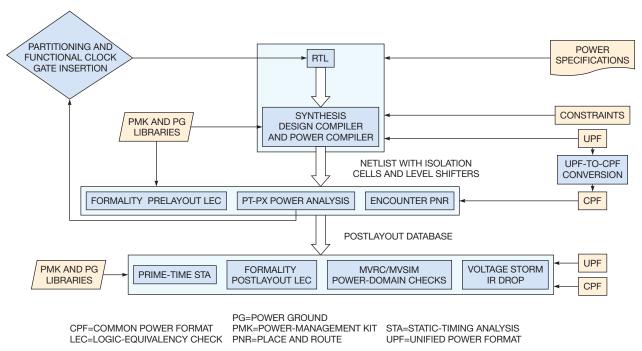

# Altering the SOC-design flow

Powerful forces are at work, resculpting SOC-design methods into new shapes.

By Ron Wilson, Executive Editor

# EDN 6,10,10 contents

# Low power: a chip and system-design primer

24 Parsing through the conflicting power-consumption claims of various microcontroller vendors can be challenging. For most applications, a duty-cycle-determined fundamental power-consumption equation can easily cut through the clutter.

By Mike Salas, Silicon Labs

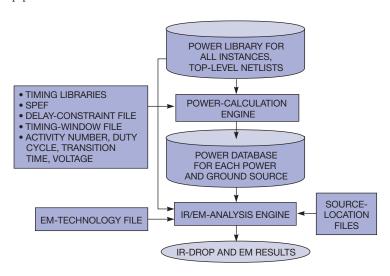

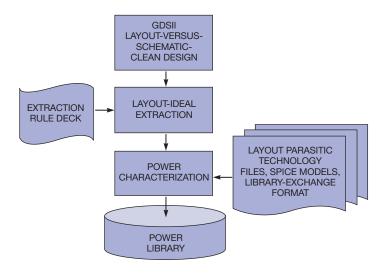

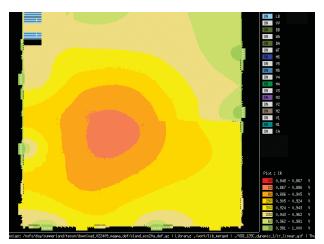

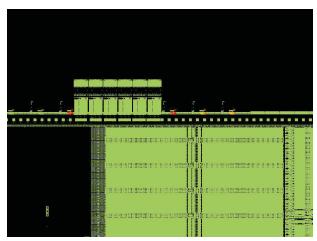

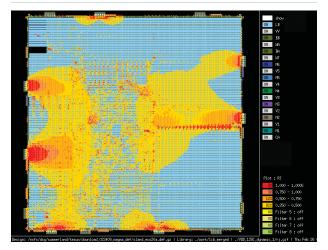

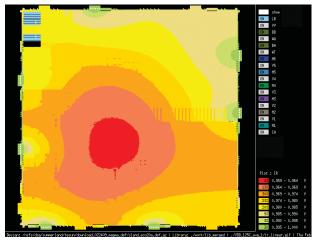

# Power-grid analysis on SOC-graphics-chip design

36 You can successfully run power-grid analysis on a 65-nm mixed-signal SOC design.

By Ravi Poddar, PhD, and Ted Sun, Integrated Device Technology Inc

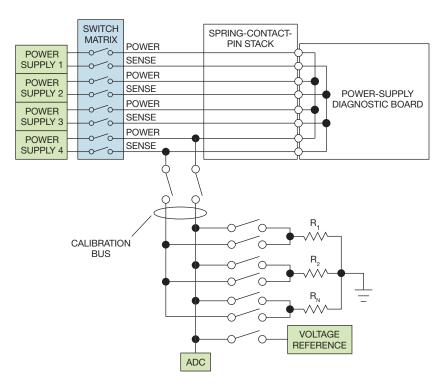

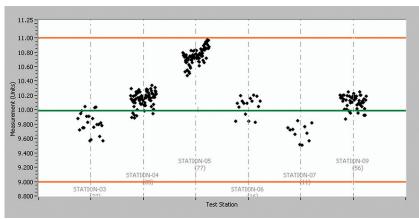

# Test your testers for R&R

Periodic checks of your tester's reliability and repeatability minimize the chance of false test results.

By Martin Rowe, Senior Technical Editor, Test & Measurement World

- 12 JFET op amps suit use in professional-audio applications

- 12 20-bit DAC simplifies MRI-signal path

- 14 Adlink introduces Atom-based SBCs

- 14 Digital PFC IC ups performance, shrinks parts count and price

- 16 LeCroy debuts embedded-test tools

- 16 Three-phase, step-down dc/dc controller targets high current rails

- 18 Backplanes target embedded-system designs

- 18 PMC goes multicore with RAID controller

- 19 Gold-covered "microlens" could be breakthrough in infrared imaging

- 19 Kozio highlights validation and test software

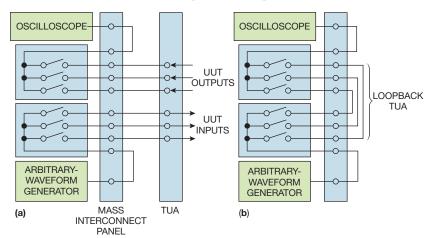

# User-configurable FPGA modules boost PXI-system versatility

44 FPGA performance and configurability are becoming available to system developers and end users, adding a new range of design possibilities.

By Richard A Quinnell, Contributing Technical Editor

# DESIGNIDEAS

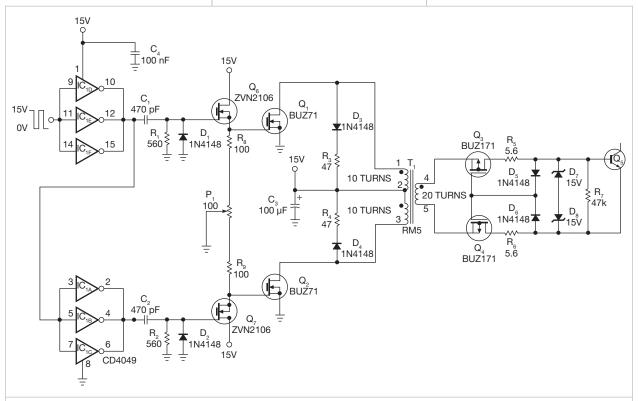

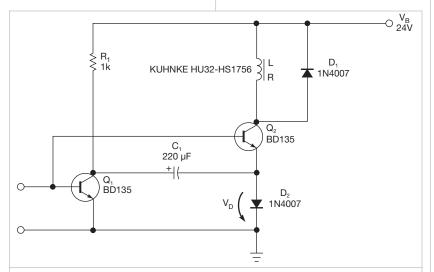

- 47 Isolated FET pulse driver increases power rate and duty cycle

- 50 Detect missing pulses to avoid losing data

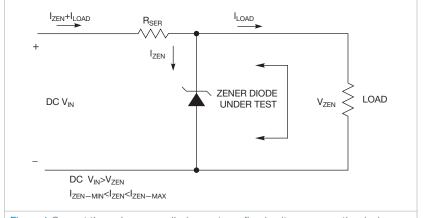

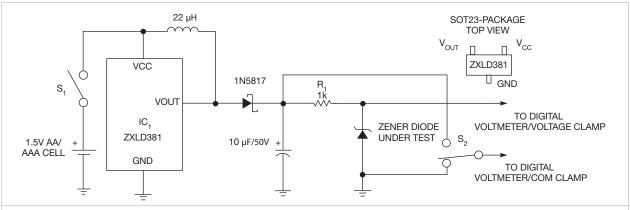

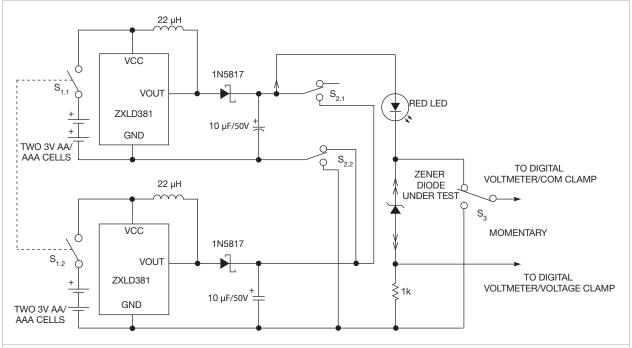

- 51 Circuit lets you measure zener voltages and test LEDs

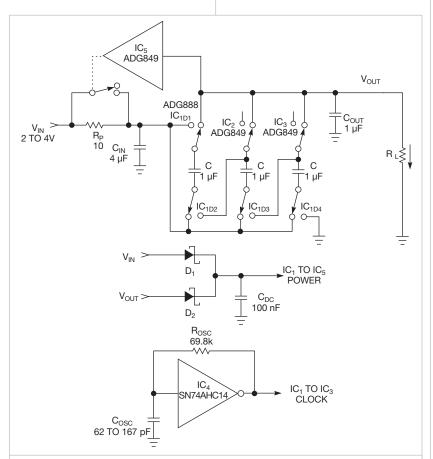

- 52 Switched-capacitor voltage multiplier achieves 95% efficiency

- 54 Bootstrap circuit speeds solenoid actuation

### "I need a faster, more accurate audio analyzer."

## We knew you'd say that.

The new Agilent U8903A audio analyzer is four times more accurate and over seven times faster than its popular HP 8903B ancestor. In fact, it is among the fastest and most accurate currently in its class. It's also a more fully capable audio analyzer, letting you make crosstalk measurements and phase measurements, FFT analysis, and graph sweep. That's taking it to the next level. That's Agilent.

Learn how to migrate effortlessly - Free application note filled with tips www.agilent.com/find/AgilentU8903A

u.s. 1-800-829-4444 canada: 1-877-894-4414

#### contents 61010

#### **DEPARTMENTS & COLUMNS**

- 9 EDN.comment: The crash of 2:45 pm, network theory, and the future of SOC design

- 22 Signal Integrity: 7% solution

- 55 Product Roundup: Power Sources, Sensors/Transducers, Connectors

- 58 Tales from the Cube: An old PAL saves the day

#### **EDN** online contents

www.edn.com

#### **ENGINEERS' TRUE STORIES**

In EDN's Tales from the Cube, engineers relate their most vexing design challenges— and how they conquered them. Here are

some examples of how your peers solved real-world problems:

#### The turn of the screwdriver

→www.edn.com/100610toca

#### Sting like a bee

→www.edn.com/100610tocb

#### Can't put a Band-Aid on a boomerang

→www.edn.com/100610tocc

#### Seeing red over dead LEDs

→www.edn.com/100610tocf

Read more in the Tales archive at www.edn.com/tales.

#### FROM EDN's BLOGS

Desolder SMD ICs with bismuth solder From Anablog, by Paul Rako When I wrote my article on prototyping, I learned that one way to desolder chips

and such is to melt some bismuth solder into the solder joints.

→www.edn.com/100610tocd

Smart-grid chips integrate functions as meter vendors aim for standards From PowerSource,

by Margery Conner

Freescale has fleshed out

its smart-power-meter-IC family with the announcement of the MC9S08GW64, which integrates gas- and water-metering functions. The chip, based on an 8-bit S08 core, includes an electricity-metering analog front end with two independent 16-bit SAR ADCs and a programmable delay block for phase-error compensation.

→www.edn.com/100610toce

EDN® (ISSN#0012-7515) is published semimonthly, 24 times per year, by Canon Communications LLC, 11444 W. Olympic Blvd., Los Angeles CA 90064-1549; 310/445-4200; FAX 310/445-4299. Periodicals postage paid at Los Angeles, California, and at additional mailing offices. SUBSCRIPTIONS—Free to qualified subscribers as defined on the subscription card. Rates for nonqualified subscriptions, including all issues: US, \$150 one year; \$250 two years; \$300 three years. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For telephone inquiries regarding subscriptions, call 763/746-2792. Email: EDN®kmpsgroup.com. CHANGE OF ADDRESS—Notices should be sent promptly to PO Box 47461, Plymouth, MN 55447. Please provide old mailing labels as well as new address. Allow two months for change. NOTICE—Every precaution is taken to ensure accuracy of content; however, the publisher cannot accept responsibility for the correctness of the information supplied or advertised or for any opinion expressed herein. POSTMASTER—Send address changes to EDN, PO Box 47461, Plymouth, MN 55447. Canada Post: Publications Mail Agreement 40612608. Return undeliverable Canadian addresses to Pitney Bowes, Inc., PO Box 2542, London, ON N6C 6B2. Copyright 2010 by Canon Communications LLC. All rights reserved. Reproduction in whole or part without written permission is prohibited. Volume 55, Number 11 (Printed in USA).

# Simpler Power Conversion

IR's AC-DC product portfolio offers simple, compact high density solutions tailored for energy-efficient power supplies.

#### µPFC™ PFC IC

| Part<br>Number     | Pckg.         | V <sub>cc</sub><br>(V) | Freq.<br>(kHz) | Gate<br>Drive<br>±(A) | V <sub>GATE</sub><br>Clamp<br>(V) | Current<br>Mode |

|--------------------|---------------|------------------------|----------------|-----------------------|-----------------------------------|-----------------|

| IR1150<br>(STR)PbF | SO-8<br>PDIP8 | 13-22                  | 50-200         | 1.5                   |                                   | ССМ             |

| /                  |               |                        |                |                       |                                   |                 |

#### **SmartRectifier™ IC**

|  | Part<br>Number                 | IR1166S<br>PbF | IR1167AS<br>PbF | IR1167BS<br>PbF | IR1168S<br>PbF |  |  |

|--|--------------------------------|----------------|-----------------|-----------------|----------------|--|--|

|  | Package                        | \$0-8          |                 |                 |                |  |  |

|  | V <sub>cc</sub> (V)            | 20             |                 |                 |                |  |  |

|  | V <sub>FET</sub> (V)           | <=200          |                 |                 |                |  |  |

|  | Sw Freq.<br>max (kHz)          |                |                 |                 |                |  |  |

|  | Gate Drive<br>±(A)             | +1/-4          | +2              | +1/-4           |                |  |  |

|  | V <sub>GATE</sub> Clamp<br>(V) | 10.7           | 10.7            | 14.5            | 10.7           |  |  |

|  | Min. On Time<br>(ns)           | Pi             | 750             |                 |                |  |  |

|  | Channel                        |                | 2               |                 |                |  |  |

|  | RoHS                           | V              |                 | ~               |                |  |  |

For more information call 1.800.981.8699 or visit

www.irf.com

International

Rectifier

THE POWER MANAGEMENT LEADER

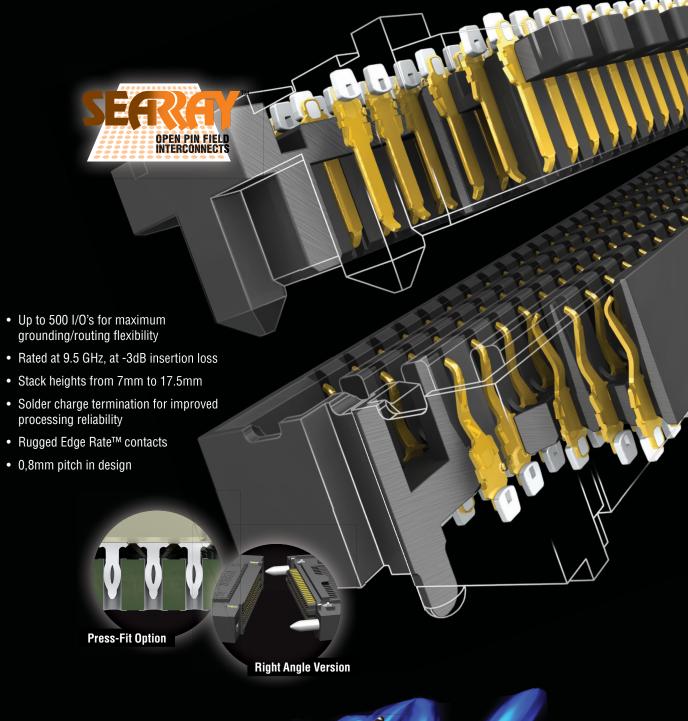

# DENSE. FAST. FLEXIBLE.

ine Solutions

www.samtec.com/searay

#### BY RON WILSON, EXECUTIVE EDITOR

### The crash of 2:45 pm, network theory, and the future of SOC design

s the May 6 New York Stock Exchange trading event passes from hard news into the hands of the television experts, most fingers are pointing at an erroneous trade that suddenly dumped an absurd number of shares for sale onto the market, causing the loss of more than 1000 points on the Dow in less than a half-hour. Computer programs order most of the NYSE trades, however, and humans never see them, so I think we need to consider another line of inquiry.

The data centers that run these algorithmic trading programs connect to even bigger data centers that log, execute, and report the trades. These connections are low-latency because a change of a few microseconds in the round-trip latency can change the income or loss an algorithm generates at a node. This loss can be enough to drive banks to pay a lot for slightly faster hardware. Further, the data centers can connect to places other than the trading hub, including to each other.

| 3  | 1986           | 37.52          | 17.12          | 0.75 -1.81%                   |

|----|----------------|----------------|----------------|-------------------------------|

|    | 17.47          | 17.02<br>40.86 | 42.15          | 10 13 0.48%                   |

|    | 27.15          | 26.07          | 27.09<br>22.47 | -n 46 -2.U9%                  |

|    | 22.59          | 21.71<br>22.74 | 23.37          | -1.26 -5.12%                  |

|    | 391.70         | 377.43         | 391.66         | -12.51 -3.30%<br>-0.74 -0.78% |

| 15 | 95.67<br>25.32 | 93.96<br>24.74 | 95.61<br>25.22 | -0.74 -0.78%<br>-0.42 -1.69%  |

| 1  | 24.89<br>57.55 | 24.35          | 24.82          | +0.30 1.22%                   |

|    | 41.00          | 30,00          | 57 27          | 0.00                          |

This situation represents a mesh network in which the topology is undocumented and dynamic. The variability in link latencies is sufficient to influence the behavior of the nodes. Except for the exchanges at the hubs, the algorithm running at each node is secret from every other node, and even its authors may not fully understand it. In other words, these data centers contain a recipe for a dynamically unstable network that no one can analyze.

These networks have few stability mechanisms. One is the hypothetical tendency for free markets to discover the current fair value of a commodity. In principle, this tendency should lead the networks to converge on "fair" prices for stocks. Analysts have not studied this hypothesis in cases in which the agents in the market are algorithms that should outsmart each other. The other stability mechanism is the willingness of humans to put an artificial brake on trading speed when they become frightened. But such a decision takes tens of minutes.

In this incomprehensible, unstable network with only weak and glacially slow controls, you would expect just the sort of behaviors we are starting to see: local oscillations and limit cycles and the occasional global instability.

According to Carnegie Mellon University Professor Jeannette Wing, assistant director for CISE (computer and information science and engineering) at the National Science Foundation, the world faces an analogous problem with global information networks of all sorts: We just don't know how they behave. One of the challenges most interesting to Wing's branch of the NSF is to see the construction of a theory of large networks so we can begin to understand them.

What does this information have to do with SOCs (systems on chips)? As

Without a useful theory of network behavior at the chip level, we may be unable to model SOCs well enough to predict what they will do in a system.

we move deeper into heterogeneous multicore SOCs, we are beginning to build large on-chip networks that have mesh organization and nondeterministic latencies. They also have algorithmic nodes. Only the IP (intellectual-property) provider that created these nodes may know about their actual operation. These nodes will compete for shared memory, interconnect quality of service, and—in the future—power.

Without a useful theory of network behavior at the chip level, we may be unable to model SOCs well enough to predict what they will do in a customer's system. Unless we develop such a theory for financial networks, however, our ability to design SOCs won't much matter.EDN

Contact me at ronald.wilson@cancom.com.

# Support Across The Board.

From Design to Delivery<sup>™</sup>

#### Now, you can have it all.™

Faster and easier than ever before. Our commitment to customer service is backed by an extensive product offering combined with our supply chain and design chain services – which can swiftly be tailored to meet your exact needs. We have dedicated employees who have the experience to provide the highest level of customer service with accuracy and efficiency. All of our technical experts are factory certified on the latest technologies, providing you the expertise to move projects forward with speed and confidence.

Avnet offers the best of both worlds: extensive product and supply chain knowledge, and specialized technical skill which translates into faster time to market – and the peace of mind that comes from working with the industry's best. Avnet is ranked Best-In-Class\* for well-informed sales reps, knowledgeable application engineers and our design engineering services – proof that we consistently deliver:

- > Industry recognized product expertise

- > Specialized technical skills

Ready. Set. Go to Market.™

Visit the Avnet Design Resource Center™ at: www.em.avnet.com/drc

Accelerating Your Success\*\*

1 800 332 8638 www.em.avnet.com

# **EDN**

#### PUBLISHER, EDN WORLDWIDE

Russell E Pratt, 1-781-869-7982; russell.pratt@cancom.com

#### ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes, 1-925-736-7617; judy.hayes@cancom.com

#### EDITOR-IN-CHIEF, EDN WORLDWIDE

Rick Nelson, 1-781-869-7970; richard.nelson@cancom.com

#### **EXECUTIVE EDITOR**

Ron Wilson, 1-510-744-1263; ronald.wilson@cancom.com

#### MANAGING EDITOR

Amy Norcross

1-781-869-7971;

fax: 1-781-862-4853;

amy.norcross@cancom.com

Contact for contributed technical articles

#### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@cancom.com

#### MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-760-0159; brian.dipert@cancom.com

#### **NEWS**

Suzanne Deffree, Managing Editor 1-631-266-3433; suzanne.deffree@cancom.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; margery.conner@cancom.com

#### DESIGN IDEAS EDITOR

Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@cancom.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville 1-781-734-8439; fax: 1-781-862-4853; f.granville@reedbusiness.com

#### CONSULTING EDITOR

Jim Williams, Staff Scientist, Linear Technology edn.editor@cancom.com

#### **CONTRIBUTING TECHNICAL EDITORS**

Dan Strassberg, strassbergedn@att.net Robert Cravotta, robert.cravotta@embeddedinsights.com

#### **COLUMNISTS**

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap Kevin C Craig, PhD, Marquette University

#### LEAD ART DIRECTOR

Marco Aguilera

#### ASSOCIATE ART DIRECTOR

Tim Burns

#### **PRODUCTION**

Michael Ciardiello, Director of Premedia Technologies Jeff Tade,

> Production Director Brian Wu,

Publications Production Manager Jeff Polman, Derric Treece, Senior Production Artists William Baughman, Ricardo Esparza, Production Artists

#### **EDN EUROPE**

Graham Prophet, Editor, Reed Publishing +44 118 935 1650; gprophet@reedbusiness.fr

#### EDN ASIA

Luke Rattigan, Chief Executive Officer luke.rattigan@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

#### **EDN CHINA**

William Zhang, Publisher and Editorial Director wmzhang@rbichina.com.cn Jeff Lu, Executive Editor

jefflu@rbichina.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

## EXECUTIVE OFFICERS Charles G. McCurdy, Chief Executive Officer

Fred Gysi,

Chief Financial Officer

Mike Deering,

Chief Technology Officer

Ron Wall,

Senior Vice President, Publications

Kevin O'Keefe,

Senior Vice President, Events Division

Roger Burg,

Vice President, Operations

Jason Brown.

Vice President, E-media

EDN. 33 Hayden Avenue, Lexington, MA 02421. www.edn.com. Subscription inquiries: 1-763-746-2792; EDN@kmpsgroup.com. Address changes: Send notice promptly to PO Box 47461, Plymouth, MN 55447. Please provide an old mailing label as well as your new address. Allow two months for the change. Canon Communications LLC, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 1-310-445-4200; fax: 1-310-445-4299.

# MAXIMUM

### RELIABILITY

In contact, stability and low-noise performance

Mill-Max Mfg. Corp. spring-loaded connectors provide superior reliability under the most rigorous environmental conditions, offering:

- · Continuous, low-noise electrical connections.

- Spike-free stability to 50G shock and 10G vibration.

- Continued high performance through 1,000,000+ cycles.

- Low- and high-profile surface-mount styles.

- 45 discrete designs for customer-specific assemblies.

- 6 families of single and double strip assemblies.

- The shortest production lead times in the industry.

SLC Connector Assemblies

Stay in contact with Mill-Max spring-loaded connectors.

To view our Design Guide, new product offerings and request a datasheet with free samples, visit

www.mill-max.com/EDN596

# JFET op amps suit use in professional-audio applications

exas Instruments' Burr-Brown Division recently released the single OPA1641, dual OPA1642, and quad OPA1644 operational amplifiers, which feature a JFET input stage. The parts operate with ±2.25 to ±18V power supplies, and output distortion is 0.00005% at 1 kHz. The devices feature a ±20-pA maximum bias current at 25°C and a 70-pA typical

The OPA1641 JFET op amp features low noise and small input bias currents, suiting use as an amplifier on the outputs of an audio codec.

bias current at 85°C. The 11-MHz-bandwidth IC has less than 3.5-mV maximum offset voltage. It consumes 1.8 mA quiescent current per channel and achieves a 20V/µsec slew rate. The amp is unity-gain stable and has an open-loop gain of 105 dB. The rail-to-rail output has a 2-k $\Omega$  load. The amplifiers have 5.1-nV/ $\sqrt{\rm Hz}$  voltage noise at 1 kHz and 8 nV/ $\sqrt{\rm Hz}$  at 10 Hz.

Because JFETs are buried devices, they are not subject to noise that surface defects create. These amplifiers' JFETs also feature a flickernoise corner of less than 20 Hz, making them ideal for professional-audio applications. The low bias-current inputs also suit them for use with signals having high source impedance.

The single-channel OPA1641 is available in an SO-8 package for 95 cents (1000). The two-channel OPA1642 is available in an SO-8 or an MSOP-8 package for \$1.45, and the four-channel OPA1644 is available in an SO-14 or a TSSOP-14 package for \$1.95.

-by Paul Rako

>Texas Instruments, www.ti.com.

#### - FEEDBACK LOOP

"As I understand

'The Bumblebee

Myth,' the bumblebee was proved

to have insufficient wing area

to enable it to

fly. However, the

equations used

were the ones

used for fixedwing aircraft! And

the bumblebee's

wings do, indeed,

move!"

—Computer geek and *EDN* reader Paul E Musselman, in *EDN's* Feedback Loop, at www.edn.com/article/457778-Sting\_like\_a\_bee.php. Add your comments.

#### 20-bit DAC simplifies MRI-signal path

nalog Devices' new AD5791 DAC has better performance and uses fewer parts in MRI (magnetic-resonance-imaging) equipment than other methods targeting this application. It also finds use in process control; data-acquisition systems; source-measurement units; and general analog applications, such as digital gain and offset adjustment, programmable-voltage and -current sources, and programmable attenuators.

The device offers a maximum-relative-accuracy specification of  $\pm 1$  LSB, guaranteed monotonic operation with a  $\pm 1$ -LSB-maximum DNL (differential-nonlinearity) specification, 0.025-ppm low-frequency noise, and 0.05-ppm/°C output drift. The spectral-noise density is 9 nV/ $\sqrt{\text{Hz}}$ , and settling time is 1 µsec. You can configure

the output for standard unipolar 5 and 10V or bipolar  $\pm 5$  and  $\pm 10$ V ranges. The device operates from a 33V bipolar power supply and consumes 4.2 mA of current on the analog power pins and 800 mA on the digital power pin. It directly drives a 60-k $\Omega$  load, eliminating linearity and noise degradation that are the drawbacks of output-buffering op amps. The AD5791 uses a three-wire serial interface that operates at clock rates as high as 50 MHz.

The part comes in 24-pin LFCSPs and 20-pin TTSOPs, operates over a -40 to +105°C temperature range, and has a suggested retail price of \$38 (1000). Samples are available now, and production quantities will become available in August 2010.

-by Paul Rako

▶ Analog Devices, www.analog.com.

# MEET THE GUY that ELIMINATED HIS TEAM'S MANUFACTURING VARIABILITY ISSUES.

FIX YOUR MANUFACTURING VARIABILITY PROBLEMS AND YOUR REPUTATION WILL PRECEDE YOU. If you're designing chips for high functionality, high speed and lower power consumption at the most advanced process nodes, you've got variability issues. We have the solution that will increase your yield, performance and prestige by a wide margin. | Get more information at mentor.com/solutions/manufacturing-variability.

#### Adlink introduces Atom-based SBCs

dlink Technologies has introduced two SBCs (single-board computers) that it based on versions of Intel's (www. intel.com) Atom processor. The new EPIC (embedded platform for industrial computing) SBC, the Ampro ReadyBoard 740, integrates a

dual-core Atom D510 or a singlecore Atom D4 10 processor; the Ampro Core-Module 740SFF (small-form-factor) PC/104-Plus uses the Atom N450 processor.

The ReadyBoard 740's 1.66-GHz processor includes an Intel ICH8M chip set, an onboard solid-state drive. an H.264 hardware video decoder, networking capability, and I/O functions. One SO-DIMM accommodates as much as 2 Gbytes of 667-MHz DDR2 RAM. The board targets use in applications in harsh environments that require high-end video performance, such as vehicle computing platforms, self-service kiosks, digital signage, and video surveillance.

Adlink's optional MiniModule PWR power-protection module adapts the board to meet the demands of in-vehicle power environments. MiniModule PWR accommodates wide input-voltage ranges and offers reversebattery and overvoltage protection. The board has an operating-temperature range of -20 to +70°C; prices start at \$410.

The ReadyBoard 740's 1.66-

GHz processor includes an

Intel ICH8M chip set, an

onboard solid-state drive,

an H.264 hardware video

ity, and I/O functions.

decoder, networking capabil-

The CoreModule 740 utilizes

the Atom's two-chip architec-

ture with integrated memory

to provide a balance of power

consumption and perform-

ance. The module is suitable

for use in sealed enclosures

and combines legacy I/O inter-

faces, including ISA (industry-

standard architecture), IDE

(integrated device electronics),

and serial and parallel ports

with onboard video, 1 Gbyte of

soldered RAM, and USB (Uni-

tems without the need for a custom carrier board. The CoreModule 740 also provides an upgrade path for the base of PC/104 system designs. Prices start at \$400

Adlink also announced a program to assist companies in migrating from products affected by Intel's recent product-change notifications, announcing the discontinuance of key embedded processors and chip sets.

Adlink will help its customers extend product life cycles, review customer application-system architectures, provide recommendations for upgrade paths, provide gap analysis, and offer level drop-in replacement boards.

-by Rick Nelson

www.adlinktech.com.

versal Serial Bus) 2.0 and the PCI (Peripheral Component Interconnect) bus, in a 90×96mm footprint.

The PC/104-Plus stackable form factor allows OEMs in military, avionics, transportation, data-logging, portable-computing, and other rugged applications to

> add an Intel Architecture controller to their sys-

(OEM quantities).

**►Adlink Technologies**,

#### Dilbert By Scott Adams

SOMEHOW I THINK THE MARKETING TEAM CAN SURVIVE ONE MEETING WITHOUT ENGINEERING SUPPORT.

WE'LL INCLUDE A PET GERBIL IN EVERY BOX. WE JUST NEED TO MAKE SURE IT'S IN A SEALED PLASTIC BAG SO IT WON'T CHEW ON THE CABLES.

#### DIGITAL PFC IC UPS PERFORMANCE. SHRINKS PARTS COUNT AND PRICE

Digital chips continue to encroach on traditionally analog parts of power management. For example, Cirrus Logic recently announced what it claims is the first integrated, high-volume IC for digitally controlled PFC (power-factor correction). The DCM (discontinuousconduction-mode), active-PFC CS1500 and CS1600 ICs target power supplies that operate 300W or less. The CS1500 addresses power supplies for applications such as laptops, digital TVs, and PCs, and the CS1600 targets electronic lighting ballasts.

At prices of approximately 30 cents each (high volumes), the chips compare in price with analog PFC ICs but require 30% fewer additional components and parts for EMI (electromagneticinterference) filtering. The power factor, which varies with the input line voltage and with load, is greater than 0.95.

-by Margery Conner Cirrus Logic, www.cirrus.com.

Weighing less than 6.2 lbs, the FieldFox 4- and 6-GHz, two-port VNAs boast a novel internal-calibration system.

# The Power Behind the Green

High-efficiency, high-density power conversion

Call 800-735-6200 to learn more about the power of Vicor technology.

#### LeCroy debuts embedded-test tools

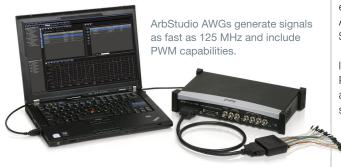

eCroy recently introduced the ArbStudio AWGs (arbitrary-waveform generators) and Logic-Studio 16 logic analyzer at the Embedded Systems Conference (www.embedded.com), which took place in April in San Jose, CA. The ArbStudio AWGs generate signals as fast as 125 MHz and include PWM (pulse-

width-modulation) capabilities. The software interface that controls the hardware simplifies waveform creation with a navigation tree that allows easy access to all channels.

The ArbStudio series includes four models: two- and four-channel versions with analog-wave-form capabilities plus two- and four-channel versions offering a combination of analog-wave-

form- and digital-pattern-generation capabilities. The four-channel models have an expansion port that allows you to connect as many as eight units. All models have a 125-MHz bandwidth, 1G-sample/sec maximum sample rate, 2M-point/channel memory, and 16-bit resolution. The instruments support both true arbitrary and DDS (directdigital-synthesis) technologies. ArbStudio software runs on an external PC. The base price for ArbStudio ranges from \$2490 to \$4990.

The LogicStudio 16 brings logic-analyzer functions to a PC, providing 16 channels with a sample rate of 1G sample/ sec and maximum input frequency as high as 100 MHz. LogicStudio 16 software

provides a dynamic waveform display with an intuitive user interface.

Tools for digital debugging include timing cursors, zooming and panning functions, a persistence display, and a history mode that can replay old data captures. LogicStudio supports protocol analysis for I<sup>2</sup>C (interintegrated-circuit) interfaces, SPIs (serial-peripheral interfaces), and UART (universal asynchronous-receiver/transmitter) interfaces. It can trigger on bus addresses or data packets.

LogicStudio provides a communication link to LeCroy's WaveJet oscilloscope, thereby turning a PC into a mixed-signal debugging environment. The base price for LogicStudio 16 is \$990.—by Rick Nelson

**▶LeCroy**, www.lecroy.com.

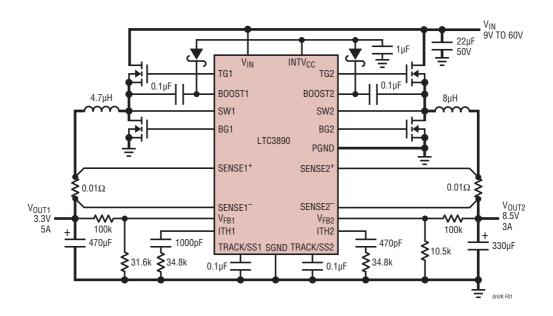

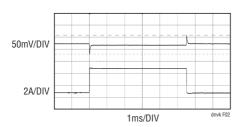

# Three-phase, step-down dc/dc controller targets high current rails

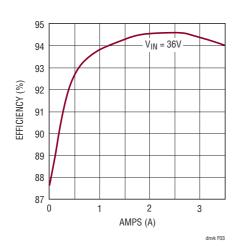

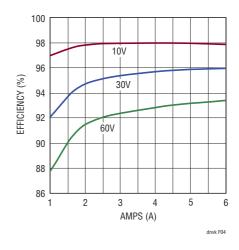

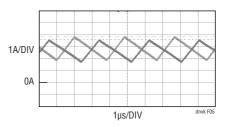

inear Technology's new three-phase, single-output LTC3829 synchronous step-down dc/dc controller features efficiency as high as 95%, PolyPhase operation, differential output-voltage sensing, and integrated PLL (phase-locked-loop) clock synchronization. You can parallel as many as six phases and clock them out of phase to minimize input- and output-filtering requirements for applications requiring currents as high as 150A.

The differential amplifier provides true remote output-voltage sensing of both the positive and the negative terminals, enabling high-accuracy regulation independent of IR losses in trace runs, vias, and interconnects. Applications include high-current ASIC and FPGA supplies, power-distribution buses, and high-power audio amplifiers.

The LTC3829 operates with all N-channel MOSFETs from input voltages of 4.5 to 38V, and it can produce  $\pm 0.75\%$ -accurate output voltages of 0.6 to 5V. You can ascertain the output current by monitoring the volt-

age drop across the output inductor's DCR (dc resistance) or by using a sense resistor. Programmable DCR temperature compensation maintains an accurate and constant current-limit setpoint over a broad temperature range. Onboard gate drivers minimize MOSFET switching losses and allow the use of multiple MOSFETs that connect in parallel. You can program a fixed operating frequency of 250 to 770 kHz or synchronize the frequency to an external clock with the internal PLL. The device's minimum ontime of 90 nsec makes it ideal for high-step-down-ratio applications.

The LTC3829 incorporates an adjustable "stage-shedding" technique to increase light-load efficiency by eliminating the gate-charge and switching losses of two of its output stages. You can also configure the LTC3829 controller for adjustable burst-mode operation, producing higher efficiency at light loads. A nonlinear control mode is optional and improves load-step transient response. Adaptive voltage positioning minimizes the maximum transient

voltage deviation during a step load.

Tracking and sequencing functions allow the optimization of power-up and powerdown of multiple power supplies. Additional features include current-mode control, an onboard low-dropout regulator for IC power,

The three-phase, single-output LTC3829 synchronous step-down dc/dc controller features efficiency as high as 95%.

programmable soft start, a power-good output, and an external power supply.

The LTC3829 is available in thermally enhanced, 38-lead TSSOP or 38-lead, 5×7-mm QFN packages and operates over a -40 to +125°C operating junction-temperature range, with prices starting at \$3.71 (1000). — by Fran Granville

**▶Linear Technology**, www.linear.com.

# Compact high power

Industrial or Medical

**MHP** Series

650 W

- 650 & 1000 Watt Models

- Rugged Industrial Construction

- Medical Safety Approvals (MHP range)

- Top or End Fan & 'U' Channel Options on 650W

- -20 °C to +70 °C Operation

- Variable Fan Speed for Noise Reduction

- 5 V Standby

- AC OK, Remote On/Off & Active Current Share

- 3 Year Warranty

D Photo

Call or visit our website to request a copy of our Power Supply Guide 09/10 and see our complete line of power products.

Toll free: 1-800-253-0490 nasales@xppower.com

#### Backplanes target embedded-system designs

t the ESC (Embedded Systems Conference, www.embedded. com) held in April in San Jose, CA, National Instruments took aim at helping designers integrate PXI (Peripheral Component Interconnect extensions for instrumentation) and CompactPCI (Peripheral Component Interconnect) instruments into their embedded systems by introducing board-level backplanes. The backplanes, previously available only as part of NI's PXI/CompactPCI and PXIe (PXI Express) chassis, allow OEMs to create their own custom, rugged enclo-

New backplanes from National Instruments allow OEMs to create their own custom, rugged enclosures that can accommodate PXI, PXI Express, CompactPCI, and CompactPCIe modules.

sures that can accommodate PXI, PXIe, CompactPCI, and CompactPCIe modules.

The more than 10 new 3U and 6U backplanes offer four to 18 slots. Engineers can design custom installations and enclo-

sures around the backplanes and integrate more than 1500 PXI modules, including dataacquisition cards; FPGA-based I/O modules; high-end instruments, such as signal generators and RF-signal analyzers; and a variety of bus-interface modules, including serial, MIL-STD (military standard)-1553, IEEE 1588, Profibus, and Device-Net versions.

Designers are able to use the NI LabView graphical-system-design platform to design, prototype, and deploy all aspects of their systems, in keeping with a focus on letting domain experts in robotics, medical, and energy industries, for example, play a significant role in embedded-system designs, says Casey Weltzin, NI's LabView real-time product manager.

—by Rick Nelson ▶National Instruments, www.ni.com.

#### PMC goes multicore with RAID controller

ulticore SOC (system-on-chip) architectures are gradually seeking out the spectrum in which no other way exists to reach the desired performance level, but also in midrange applications, in which several small cores can be cheaper and more

PMC-Sierra's new line of RAID-controller ICs, a joint development with IBM (www. ibm.com), features a multithreaded version of IBM's RAID firmware stack and a low-profile, eight-lane PCIe Generation 2 card to plug into x86 servers.

energy-efficient than one fire-breathing CPU. Consequently, embedded-application developers are wrestling their code into multiple threads, and SOC developers are providing cores to match the threads.

A case in point, as PMC-Sierra recently

announced, is a RAID (redundant-array-of-inexpensive-disks) controller. This application might not seem computationally intensive, but, as Cameron Brett, PMC-Sierra's product-marketing manager, points out, the plummeting price of NAND flash is changing the picture.

Consider a high-performance RAID of, say, 20 rotating drives. If you want performance, you will use the drives in short-stroke mode-that is, employing only the outermost tracks, on which the data rate is highest and you can minimize seek time. That approach gives you good performance, but you use less than 10% of each drive's raw capacity. For about the same price, you could get four 100-Gbyte solid-state drives, connect them in a RAID configuration, and get about 300 Gbytes of usable capacity. The solid-state drives would slash your power consumption from more than 200W to about 10W, however, and they would increase available throughput from about 9000 to approximately 90,000 IOPS (input/output operations per second). Suddenly, the performance of the RAID controller is an issue.

PMC has responded with a new line of RAID-controller ICs, a joint development with IBM (www.ibm.com) to produce a multithreaded version of IBM's RAID firmware stack, and a low-profile, eight-lane PCle (Peripheral Component Interconnect Express) Generation 2 card to plug into x86 servers. The products target use in RAID configurations of solid-state drives, as well as conventional hard-disk-drive RAID arrays, using either SATA (serial advanced-technology attachment) or SAS (serial attached small-computer-system interface), including the 6-Gbps SAS generation, so the controller must deliver performance. "Each solid-state drive is capable of 15,000 to 30,000 IOPS," says Zaki Hassan, PMC's director of product marketing. Even with a four-drive array, this rate is significant.

To support the RAID stack at this throughput, PMC clusters three multithreaded MIPS (www.mips.com) 34k cores around a high-speed switch. The chip uses only local memory without external DRAM, Brett says. The board that uses the chip, the BR5225-80, measures in at more than 136,000 IOPS on 4000 random reads, and more than 44,000 IOPS on the 4K OLTP (online-transaction-processing) random 2-to-1 metric. Additionally, the chip supports one end of a Web-accessible, SMI-S (Storage Management Initiative Specification) 1.4-compliant management utility that runs on the host server.

-by Ron Wilson

▶**PMC-Sierra**, www.pmc-sierra.com.

# Gold-covered "microlens" could be breakthrough in infrared imaging

esearchers at Rensselaer Polytechnic University have developed a lensless, gold-covered "microlens" that they believe will lead to breakthroughs in image-signal and infrared-imaging strength. The research uses the properties of nanoscale gold to "squeeze" light into tiny holes in the surface of the device.

The study demonstrates success in enhancing the signal of an infrared detector without also increasing the noise, according to project leader Shawn-Yu Lin, professor of physics at Rensselaer and a member of the university's Future Chips Constellation and Smart Lighting Engineering Research Center.

"We have shown that you can use nanoscopic gold to focus the light entering an infrared detector, which in turn enhances the absorption of photons and enhances the capacity of the embedded quantum dots to convert those photons into electrons," he says.

Researchers establish the detection ability of an infrared

Rensselaer Polytechnic Institute Professor Shawn-Yu Lin has developed a new nanotechnology-based "microlens."

photodetector by determining how much signal it receives and dividing that signal by the noise the detector receives. Photodetectors currently employ MCT (mercury-cadmium-telluride) technology, which has a strong signal but long exposure or low-signal imaging. The study creates a plan for developing QDIPs (quantum-dot infrared photodetectors) that can outperform MCTs.

The long, flat surface plasmon QDIPs have countless holes, measuring 1.6 microns in diameter and 1 micron deep, on the surface. Approximately 50 nm of gold covers the solid surface of the structure. Quantum dots-nanoscale crystals with unique optical and semiconductor properties—fill each hole. Properties of the QDIP's gold surface help to focus incoming light directly into the microscale holes and concentrate that light in the pool of quantum dots. That concentration strengthens the interaction between the trapped light and the quantum dots and in turn strengthens the dots' ability to convert those photons into electrons. The end result is that the device creates an electric field as much as 400% stronger than the raw energy that enters the ODIP.

The effect is similar to what would result from covering each tiny hole on the QDIP with a lens but without the extra weight and the hassle and cost of installing and calibrating millions of microscopic lenses.

Lin's team also demonstrated that the nanoscale layer of gold on the QDIP neither adds noise nor affects the device's response time. "Within a few years, we will be able to create a gold-based QDIP device with a 20-fold enhancement in signal from what we have today," Lin says. "It's a reasonable goal and could open a new range of applications, from better night-vision goggles for soldiers to more accurate medical-imaging devices."

Rensselaer published the results of the study online (**Reference 1**).

—by Suzanne Deffree ▶Rensselaer Polytechnic Institute, www.rpi.edu.

#### REFERENCE

Chang, Chun-Chieh, Yagya D Sharma, Yong-Sung Kim, Jim A Bur, Rajeev V Shenoi, San-jay Krishna, Danhong Huang, and Shawn-Yu Lin, "A Surface Plasmon Enhanced Infrared Photodetector Based on InAs [Indium-Arsenic] Quantum Dots," Nano Letters, April 20, 2010, pg 1704, http://pubs.acs.org/doi/abs/10.1021/nl100081j.

#### KOZIO HIGHLIGHTS VALIDATION AND TEST SOFTWARE

Kozio recently introduced a software suite for design validation, manufacturing test, and in-field test for embedded systems. The software provides broad datapath coverage and standardized diagnostic tests across functional areas and supports fast, automatic troubleshooting. According to the company, users can save \$100,000 in test-development and debugging costs per project and see

a three-month reduction in time to market.

The suite helps PCB designers contend with increasingly complex boards. Mentor Graphics figures show, for example, that although average board sizes have decreased over the last 15 years from 101 to 75 in.², component counts have increased from 649 to 3399, the number of component pins has increased from 4214 to

13,505, and the number of pin-to-pin connections has increased from 5190 to 10,960. Meanwhile, designers are contending with tight schedules, limited resources, design and manufacturing silos, and the need to deal with remote teams.

For design validation, the tools support interactive hardware debugging, fault isolation, characterization, and regression testing. For manufacturing test, they support parallel test and IP (intellectual-property) protection, and contract manufacturers can adapt them to their needs. In the field, the tools support built-in self-test and diagnostics. The tools provide coverage of memory; data buses; user interfaces; displays; cameras; and audio, networking, and wireless functions.

-by Rick Nelson

Kozio, www.kozio.com

# **Embedded Answers**

by Robert Cravotta - EDN Embedded Master

#### Q: When does it make sense to use an RTOS or operating system?

**An RTOS can**

simplify incorporating

commodity features.

and it lets you focus

your energy on your

value add, where your

product really

differentiates itself

from other products.

A: The answer to when it makes sense to use an RTOS depends on your system's size and complexity, as well as its real-time, reliability, and interface requirements. A key benefit of using an RTOS is that it encompasses thousands of design decisions (for better or worse) and the project does not incur a delay that it would otherwise need to because the design team avoids the productivity drag of having to consider all of the trade-offs for each of those decisions. Contemporary processors and RTOSs offer coupled resources, such as memory protection units and padded cell virtualization support, which

may blur the criteria for when it is appropriate to use or avoid using an RTOS. All but the most cost or power constrained projects may be able to afford the runtime overhead associated with at least a small and fast kernel to gain the productivity benefits of using an RTOS.

Feedback from designers indicates that using an RTOS offers a unified hardware abstraction layer and a

bunch of inter-process (task) communication APIs that can make application code more portable. If you are building a system that doesn't require user input or output, and doesn't execute much code, you probably don't need an RTOS. If your project has several developers and is using industry standard I/O ports, using an RTOS will be beneficial unless you have a very simple application or you have enough time and money to write the entire product yourself and exhaustively test all the code.

Using an RTOS supports adding the capabilities that your customers demand, by incorporating additional components of the RTOS, such as support for file systems, protocol stacks, task scheduling, Ethernet, USB, wireless, web access, and touch screen GUI. An RTOS can simplify incorporating commodity features, and it lets you focus your energy on your value add, where your product really differentiates itself

from other products. An RTOS can simplify migrating to a new processor or hardware, with your software development team not having to rewrite everything for the new hardware.

It might be useful to make a distinction between a real-time "operating system" and a multi-tasking kernel. But at the heart of any RTOS is a multitasking kernel whose primary job is to schedule tasks in response to events. A system consisting of synchronous tasks can use a hand-written coroutine scheduler. When a design indicates using

> multiple asynchronous threads or of hardware abstraction.

processes rather than a simpler synchronous operation, an RTOS kernel is recommended. There is a class of not-so-well-known RTOSs that do not include a file-system or support multi-tasking in the usual way - but it delivers a reliable task scheduling service and a minimum

On the other hand, some developers indicate they would not consider using an RTOS if the project exhibits hard real-time or safety integrity requirements and any time overhead is not acceptable. If you need to demonstrate that your system has been developed to a process that conforms to a particular standard, your choices of RTOS are limited. There are a few RTOSs that are designed to be used in military/aerospace/nuclear/automotive applications, but it's more than a rubber-stamping exercise and it may require you to working closely with the RTOS vendor.

> For more answers to your **Embedded questions, visit** www.embeddedmaster.edn.com.

WHICH WINDOWS® EMBEDDED-PLATFORM CAN HELP YOU DELIVER STANDOUT DEVICES?

FIND OUT AT WINDOWSEMBEDDED.COM/DEVICESTORIES

#### SIGNAL INTEGRITY

#### BY HOWARD JOHNSON, PhD

#### 7% solution

n 1983, my mentor, Martin Graham, PhD, had me build a Wheatstone bridge for measuring the common-mode impedance of certain twisted-pair cables, now known generically as Category 3 UTP (unshielded twisted pair). My setup required some closely matched carbon-composition resistors with values accurate to within  $\pm \frac{1}{2}$ %.

The measurements would be taken at fairly high frequencies covering the 10- to 100-MHz range. At such frequencies, even the parasitic series

inductances and shunt capacitances of the resistors must match. That requirement rules out the use of trimming potentiometers to meet the stringent accuracy requirement.

I needed a few bull's eye, hit-the-spot, on-the-money, perfect resistors. Looking at the lab stock available on that day, I found no high-precision carbon-composition resistors. There were some 2% metal-film resistors in stock, but I knew that the manufacturers of those parts sometimes etched serpentine patterns in the metal film to elongate the resistor, thus increasing the parasitic series inductance to levels unacceptable for my application. Carbon-composition resistors are made in a simple cylindrical shape that is ideal for high-frequency use.

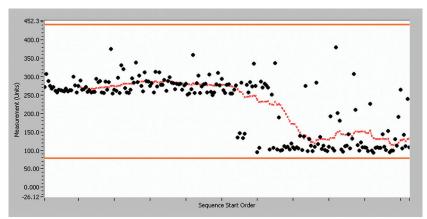

Figure 1 This histogram of 10%-resistor values reveals how 5% resistors are "made."

Imagine my surprise when, after an hour of labor and after checking 300 resistors, I found that none fell within my 1% selection window.

The only carbon-composition resistors I found had a 10% tolerance. I decided that they might work if I hand-selected values good enough for my purpose. I reasoned that out of 100 parts rated at 10% tolerance, about 10 should fall within 1% of the advertised value and that even more would do so if the distribution were centrally clumped. From those 10 parts, I hoped to select a couple of pairs suitable for my setup.

Imagine my surprise when, after an hour of labor and after checking 300 resistors, I found that none—absolutely none—fell within my 1% initial selection window.

Mathematically, if the component values were distributed evenly across the whole tolerance band of  $\pm 10\%$ , the probability of any one resistor's falling

within a ±1% selection window should be one out of 10, or 0.1. The probability of any one resistor's falling outside the selection window then equals the complement of that value, 0.9. If you repeat the experiment 300 times, the probability of all the resistors' falling outside the selection window equals  $(0.9)^{300}$ =1.8×10<sup>-14</sup>. It seemed to me inconceivable that such a low-probability event could ever actually occur in my sample of 300 parts. Monkeys striking random keys on a typewriter could more likely compose a sonnet in the mean time between experimental failures of that magnitude.

Perplexed, I sought guidance from Martin. I found him in the company cafeteria enjoying a meatloaf sandwich. On a ketchup-stained napkin, he patiently drew an odd-looking curve (Figure 1).

The drawing complete, Martin said, "A 10% carbon-composition resistor is made in a somewhat slipshod manner. The manufacturer tries to get it right, but some of the variables are just too difficult to control. They make up a batch, test them all, and then throw away the bad ones. What's left is a distribution of values truncated on either side at the ±10% limits. The other main feature of the distribution is the big gap-toothed section in the middle. That's where they pulled out all the good parts and sold them at a higher price with a  $\pm 5\%$ tolerance. How else do you think they make 5% resistors?"

My jaw hit the floor when I grasped how perfectly his explanation matched my results. He paused and then passed along another point of wisdom: "Design your circuit to use values that lie 7% away from the nominal standard values, either higher or lower, and you'll find plenty of those in the bins when you do your hand selection." EDN

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Visit his Web site at www.sigcon.com, or e-mail him at howie03@sigcon.com.

# Honeywell & TTI

– a powerful new team working for you!

Honeywell and TTI together are proud to bring you the industry leading line of sensors and switches, designed to ensure the integrity of your product.

With quality products from Honeywell and reliable, assured delivery service from TTI, you can be confident you have a total solution to meet your switch and sensor needs.

NEVER SHORT ON SOLUTIONS

1-800-CALL-TTI www.ttiinc.com

PARSING THROUGH THE CONFLICTING POWER-CONSUMPTION CLAIMS OF VARIOUS MICROCONTROLLER VENDORS CAN BE CHALLENGING. FOR MOST APPLICATIONS, A DUTY-CYCLE-DETERMINED FUNDAMENTAL POWER-CONSUMPTION EQUATION CAN EASILY CUT THROUGH THE CLUTTER.

educing power consumption has a major impact on every aspect of our lives. At a macro level, the benefits have been well-documented: lower electric bills for consumers, reduced load on utilities, and fewer batteries in landfills. In short, saving power is good for both the environment and the pocket-book. Due to the growing use of electronics worldwide, reducing power consumption must begin at the microchip level. Power-saving techniques that engineers have designed in at the chip level have a far-reaching impact, especially when involving microcontrollers that serve as the engines behind most of these electronic devices.

From a system-design perspective, identifying which microcontrollers are truly low-power requires designers to navigate through the myriad claims of various semiconductor vendors. Because of the varying and confusing metrics vendors use, this objective is a complicated task. This article briefly describes the main factors that you

need to consider when analyzing competitive microcontroller alternatives. At a basic level, you can define microcontroller power consumption as the sum of active-mode power and standby, or sleep-mode, power. However, another important metric to keep in mind is the amount of time it takes for a microcontroller to move from a standby state

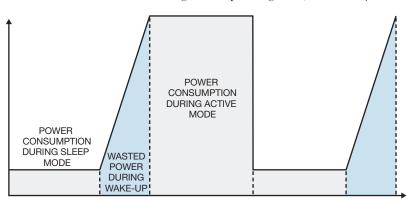

to an active state. Because the microcontroller cannot do any useful processing until all of its digital and analog components are fully settled and operational, adding in this wasted power is important when calculating total power consumption. Thus, the device's total power consumption is the sum of its active-mode power, standby power, and wake-up power.

Because every application is different, system designers have a tendency to give more weight to some of these elements than others. For example, some applications, such as water meters, spend most of their time in a standby state, so their long duty cycles require low standby-power consumption. Other applications, such as data loggers, often enter and exit active states, so it is critical to limit the time they spend in wake-up-transition modes (Figure 1). However, a vendor developing a compelling microcontroller cannot attempt to guess which of these metrics is most

# 336 Volts of Green Engineering

#### MEASURE IT - FIX IT

Developing a commercially viable fuel cell vehicle has been a significant challenge because of the considerable expense of designing and testing each new concept. With NI LabVIEW graphical programming and NI CompactRIO hardware, Ford quickly prototyped fuel cell control unit iterations, resulting in the world's first fuel cell plug-in hybrid.

#### **MEASURE IT**

#### Acquire and

Acquire and measure data from any sensor or signal

#### Analyze

Analyze and extract information with signal processing

#### Present

Present data with HMIs, Web interfaces, and reports

#### ——— FIX IT

Design

Design optimized

control algorithms

and systems

Prototype

Prototype designs

on ready-to-run

hardware

#### Prototype Deploy

Deploy to the hardware platform you choose

Ford is just one of many customers using the NI graphical system design platform to improve the world around them. Engineers and scientists in virtually every industry are creating new ways to measure and fix industrial machines and processes so they can do their jobs better and more efficiently. And, along the way, they are creating innovative solutions to address some of today's most pressing environmental issues.

>> Download the Ford technical case study at ni.com/336

800 258 7018

important but instead designs a system from the ground up that focuses on minimizing any power consumption. Accomplishing this objective requires strong mixed-signal expertise to address both the architectural-level and the circuit-level challenges necessary to minimize power in both the analog and the digital domains.

#### **ACTIVE-MODE CURRENT**

For a CMOS logic gate, the following equation yields dynamic power consumption: C×V<sup>2</sup>×f, where C is the load capacitance, V is the supply voltage, and f is the switching frequency. The capacitance term is a function of the design and processing technology, and the frequency term is a function of the application's processing requirements. However, as you can see from the equation, the supply voltage has a disproportionate impact on the overall power that the microcontroller consumes. Therefore, adding voltage regulation to the microcontroller design can yield significant active-mode-power savings by providing a lower, steady supply voltage to the microcontroller's circuitry. Switching-type converters may be a possible approach for this application, but they better suit regulator environments requiring large voltageconversion ratios. However, in batterytype applications in which the average voltage-conversion ratio approaches 1-to-1 at the end of the battery's life, a better approach would be to add an onchip low-dropout linear voltage regulator because it offers acceptable efficiency with less complexity and lower cost than a switching approach.

To illustrate the benefits of using a

#### AT A GLANCE

- Reducing power consumption must begin at the microchip level.

- Identifying which microcontrollers are truly low-power requires designers to navigate through the myriad claims of various semiconductor vendors.

- Adding voltage regulation to the microcontroller design can yield significant active-mode-power savings by providing a lower, steady supply voltage to the microcontroller's circuitry.

- An on-chip low-dropout linear voltage regulator offers acceptable efficiency with less complexity and lower cost than a switching approach.

- An innovative way to reduce power and environmental impact is to convert the design to a single-battery configuration in which the battery operates at 0.9V to the end of its useful life.

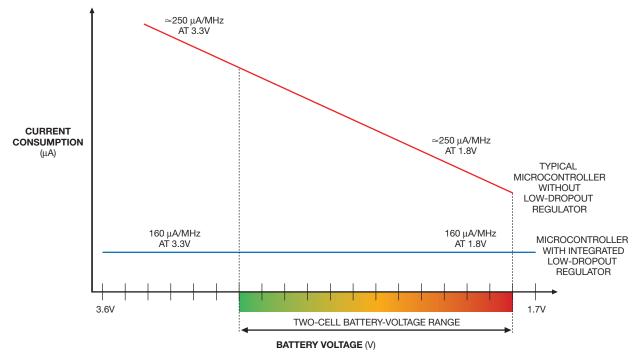

low-dropout regulator, it is helpful to restate the CMOS dynamic power equation as  $C\times V^2\times f=V\times (C\times V\times f)=V\times I$ , where the dynamic current, I, equals  $C\times V\times f$ . It is common to normalize the dynamic current to a frequency of 1 MHz and a particular supply voltage. For example, one recently introduced ultra-low-power microcontroller has a dynamic current consumption of 160 mA/MHz at 1.8V. Without supply regulation, this metric would increase to  $160\times (3.2/1.8)=284$  mA/MHz when the supply voltage is 3.2V. With a low-dropout regulator, the battery current

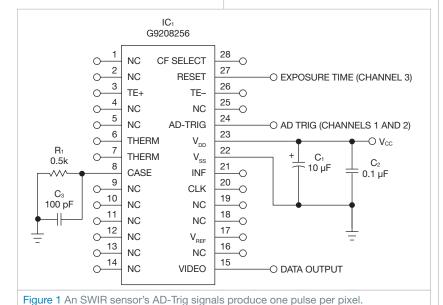

Figure 1 Curtailing wasteful wake-up latencies is critical to minimizing overall power consumption for applications that frequently move into and out of active operating modes.

remains at 160 mA/MHz across the entire supply range (Figure 2).

You can use this advanced power architecture to maintain a constant active current over the full operating-voltage range, and it can help you achieve a significant savings in power consumption. Therefore, it is important to determine the microcontroller's current consumption when operating across the entire operating-voltage range, not just at the 1.8V minimum operating condition that microcontroller vendors commonly quote. Quoting an optimistic current number that assumes anything less than a typical voltage supply does not accurately reflect how applications find use in the real world.

As an example, in systems requiring two AA or AAA coin-cell batteries, the batteries most often operate near their initial 3V voltages. Therefore, the quoted 1.8V specification can be deceiving because, from this perspective, most microcontrollers consume approximately 50% more power than the amount that their vendors commonly quote. Furthermore, because power consumption is directly proportional to switching frequency, system designers should normalize the quoted current numbers down to a current-per-megahertz basis. By combining these two factors, you can perform a side-by-side comparison of microcontrollers using current consumption per megahertz at 3V.

Some vendors attempt to confuse the issue by equating megahertz to system-clock speed when the value that is truly meaningful is instruction-clock speed. This substitution is deceiving because system clocks can operate at least twice as fast as they can execute instructions, thereby at least doubling their effective power consumption. It is therefore important to normalize specifications to instruction-clock speed. By doing so and by using a typical supply voltage, you can properly derive the actual active-mode current-consumption budget.

#### **STANDBY CURRENT**

Achieving maximum energy efficiency and, therefore, battery life requires ensuring that each microcontroller task consumes the minimum possible current at the minimum possible voltage for the shortest possible duration, so that the device spends most of its time in a low-power sleep mode. In

## The Avago Advantage

# Renewable Energy Applications: Reliability and Safety with Fiber Optic and Optocoupler Isolation Technology

#### Introduction

Climate change, rising carbon dioxide levels, environmental pollution and volatile fossil fuel prices have driven electric power generation producers, governments, and individual consumers to adopt alternative energy generation methods such as solar and wind. Governmental renewable energy support has been incorporate into strategic energy plans worldwide. During 2009 at least 73 countries had energy policy targets and more than 64 countries had policies to promote renewable power generation. Renewable energy is no longer an area dominated by research, but rather a large commercial market with high adoption and installation growth rates.

Renewable energy growth in 2008 was substantial and 2009 activity points toward continued progress. The United States ended 2008 with 25 GW of wind power, eclipsing Germany's 24 GW capacity. China's total wind power doubled for the fifth year in a row, ending the year above 12 GW, exceeding China's 2010 development target of 10 GW two years ahead of plan. More than 80 countries around the world now have commercial wind power installations.

With most 2008 offshore wind generation capacity in Europe, capacity reached nearly 1.5 GW. The United Kingdom became the offshore wind power leader in 2008 but other countries, such as the United States, have plans for new offshore facilities.

Grid-connected solar photovoltaic plants are the fastest growing power generation technology, with a 70-percent increase in existing capacity to 13 GW in 2008. This was a six fold increase in global capacity since 2004. Including off-grid applications, total 2008 photovoltaic generation increased to over 16 GW. In 2008, utility-scale solar PV power plants—plants over 200 kW—were estimated to have grown by 80%, to 1,800, since 2007. The added plants totaled over 3 GW, a tripling of existing 2007 capacity.

Utility photovoltaic plant additions were a major 2008 focus in Spain but facilities also went into the Czech Republic, France, Germany, Italy, Korea, and Portugal. New solar photovoltaic plants are planned and under development throughout Europe as well as China, India, Japan, and the United States.

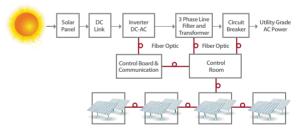

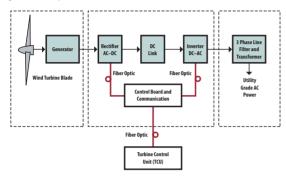

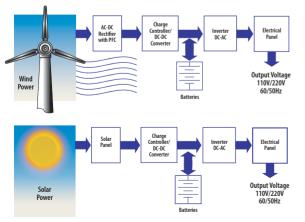

Given the high growth rates and importance of renewable energy, Avago focused its fiber optic and isolation product portfolios and product development efforts toward renewable energy applications. Digital optocouplers, gate drivers, isolation amplifiers and solid state relays provide safety isolation and insulation along with their basic function. Fiber optic components, besides providing isolation, provide EMI resistant, long distance communication channels in wind turbine farms and panel-to-panel communications in solar photovoltaic systems. These control and communication channels are critical for safety and optimal power efficiency in distributed solar systems and especially for offshore wind farm installations.

#### **Avago Renewable Energy Solutions**

Avago Technologies offers fiber optic transmitters, receivers and transceivers, as well as IGBT and Power MOSFET gate drivers and optocoupler isolation products for wind turbine, wind farm and solar electric power generation.

Avago fiber optic components, isolated gate drivers, isolation amplifiers and digital optocouplers are deployed in wind turbines, wind farms and solar photovoltaic energy farms today.

Applications include:

- Power rectifiers and inverter power assemblies

- · Control and communication boards

- Turbine control unit condition monitoring systems

- Wind farm networks

- Sun tracking control

- Communications boards

- Solar farm substation automation and protection relays

- · Single- and three-phase inverters

- Battery chargers

- Motor control

- · DC-to-DC converters,

- · System control and monitoring

#### **Solar Energy: Fiber Optic Solutions**

Avago fiber optic transceivers provide control and communication links within a solar energy system and within the solar farm. Resistant to EMI and able to withstand rugged environments, Avago transceivers support POF, HCS and Multimode fiber. Plastic cable supports transmission up to 50 m. For longer distances 200  $\mu m$  HCS and 62.5/125  $\mu m$  fiber will support up to 2,700 m links. Maximum transmission distances, depending on data rates, are up to 80 km.

Data rates from 1/5/10/20/160 MBd are available with many different connector styles: LC, SC, SFP and MT-RJ.

Figure 1. Fiber data links in solar energy farm

### Wind Turbine Networking, Control and Communications: Fiber Optic Solutions

In wind turbine applications access for maintenance and repair is more limited than in land-based solar farms. This is especially true for off shore wind generation installations. In addition, large mechanical loads and changing local weather conditions must be monitored in near real time for optimal power generation, safety and control. Long term reliability and quality are very important component selection factors.

Inside the turbine nacelle, short range fiber optic connections connect power generation subsystems and the turbine pitch controller to the main system controller. Avago offers a broad portfolio of fiber-optics transmitter and receiver like the

#### The Avago Advantage Technical Notes

HFBR-0500Z family which are used in Wind-Turbines since many years. For Wind-Turbines >2 MW the main choice inside the turbine is fiber optics because of EMI, lightning and galvanic isolation. Longer range fiber links connect to tower base and the wind farm network.

In turbine monitoring and solar systems, Fast Ethernet transceivers with DMI and SC-RJ connectors, such as the Avago AFBR-5978Z, are popular as they operate at 650  $\mu m$  over POF and HCS cable and feature a  $-25^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  temperature range. A demonstration kit for the AFBR-5978Z (AFBR-0978Z) is available from any Avago sales offices or representative.

Our new multimode, small form factor (SFP) HFBR-57E5APZ Fast Ethernet transceiver with DMI requires only 611 mW and operates from 3.3 V.

Figure 2. Fiber optic communication links in wind turbines

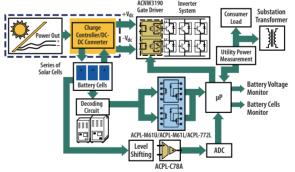

### Solar and Wind Power: Application Specific Optocouplers, Gate Drivers and Isolation Amplifiers

As the leading optocoupler supplier, Avago develops application specific isolated power MOSFET gate and IGBT drivers for power applications. Featuring high peak output current, high CMR, wide temperature range, low supply current, surface mount packages and integrated protection circuits they are ideal for motor control, inverter and battery charging circuits.

The ACNW3190 isolated gate driver has a 5 A peak drive current and under voltage lockout (UVLO) protection. Other devices have 0.4 A to 2.5 A peak drive current. For maximum reliability and design flexibility, Avago devices have protection features such as integrated VCE detection, UVLO, "soft" IGBT turn-off, isolated open-collector fault feedback and active Miller clamping for maximum design flexibility and circuit protection. A Miller clamp controls the Miller capacitance current during high dV/dt transitions and can eliminate the need for a negative supply voltage.

Figure 3. Isolation and insulation solutions in wind-solar power generation systems include inverters, charge controllers and communications.

With the Avago analog isolation amplifiers, current and voltage monitoring in motor control, inverter and battery applications is simple, safe and accurate. Phase currents and DC link voltages are easily measured while maintaining isolation. The amplifiers have working voltages of up to 1140 V for safety. Gain accuracy ranges from  $\pm 1\%$  to  $\pm 5\%$ .

The ACPL-796J 1-bit, second-order sigma-delta modulator converts an analog input signal into a high-speed data stream with galvanic isolation based on Avago's optical coupling technology. The ACPL-796J operates from a 5 V power supply with dynamic range of 80 dB with an appropriate digital filter. The differential inputs of  $\pm 200$  mV, full scale  $\pm 320$  mV, are ideal for direct connection to shunt resistors or other low-level signal sources in motor phase current measurement applications.

#### **Solar and Wind Power: Digital Optocouplers**

Wind control systems must accommodate varying wind conditions and avoid run-to-failure by monitoring subsystems accurately. High voltage isolation, current isolation and immunity to EMI are critical for reliable and robust control systems. Solar and wind farms face harsh environmental conditions and operate over large physical areas susceptible to lightning and extreme temperatures. Avago digital optocouplers have the insulation and isolation specifications to make command and control systems safe and reliable. All our digital optocouplers are qualified to all international safety organization insulation and isolation specifications. Many devices have working voltages that exceed 1768 Vrms and isolation voltage up to 7500 Vrms are offered.

Operating at 10 MBd, multi-channel and bi-directional optocouplers (ACSL-6210/6310/64x0 in Dual/Triple/Quad channel) maximize design options and conserve PCB area. For extreme environments, the ACPL-M61U features –40°C to 125°C operation. The ACPL-M61L/061L/W61L/K64L are ultra low power optocouplers suitable for energy efficient systems. Higher speed devices such as the ACPL-772L/072L operate at 25 MBd and from –40°C to 105°C.

Our photo MOSFETS, or solid state relays (SSRs), operate with voltages from 60 V to 600 V and with currents up to 2 A for energy storage management systems.

Figure 4. Isolated gate drive, digital optocoupler, level shifter and isolation amplifier applications.

#### Summary

Innovative fiber optic and optical isolation solutions have been available from Avago for over three decades. As a major contributor to the work of international standards organizations, device reliability, quality and safety are always part of any Avago design. We offer the industry's best isolation technology, specifically designed and manufactured to meet the stringent requirements of applications in power generation systems.

Around the world our customers value what we do. We provide the components and technology to make their visions for the renewable energy market expand and prosper.

some applications, the sleep-mode current is the parameter most responsible for overall energy consumption. However, engineers often overlook the fact that leakage current is the primary limitation on the absolute minimum sleep current a microcontroller can achieve. For example, a 20-input device that has an input-leakage-current specification of 100 nA could consume as much as 2  $\mu$ A of power during sleep mode.

A number of factors, the most important of which is process technology, affect leakage current. In some cases, vendors use a 0.25- or 0.35-micron process technology to reduce the leakage-induced sleep current, but this choice

**IMPLEMENT AN**

**POWER-MANAGE-**

LIMITS LEAKAGE AND

**ENABLES ULTRALOW**

**MENT UNIT THAT**

SLEEP CURRENT.

**ADVANCED**

comes at the expense of a higher active current. In other cases, microcontroller vendors use 0.18-micron or smaller process technologies to reduce active-mode current, but this choice comes at the expense of higher leakage currents. One approach to

this problem is to apply mixed-signal expertise to implement an advanced power-management unit that limits leakage and enables ultralow sleep current regardless of the underlying process technology in use. When using process technologies of 0.25 micron or smaller, minimizing sleep-mode current requires cutting power to the digital core. Modules that operate in sleep mode, such as power-management circuits, I/O-pad cells, and real-time clocks, must operate from the unregulated voltage supply to avoid burning additional current in a low-dropout regulator. Cutting power to the digital-core logic also prevents its off-state leakage from contributing to the sleep-mode current; however, the microcontroller must preserve RAM contents and the state of all registers during sleep mode so that execution can resume where it left off.

You can perform this preservation using a low-current sleep-mode latchbias scheme or retention latches that can hold the state in sleep mode without significant leakage. The microcontroller also requires some form of continuous supply-voltage monitoring,

such as brownout detection, to reset the device in the event that the supply voltage drops below the minimum retention voltage, which could corrupt the operating state. It is therefore important to examine the underlying leakage-current specifications to determine which microcontroller vendors have applied their mixed-signal expertise toward solving this complex problem.

Designers should also consider the fact that most vendors offer many standby-current options. Most suppliers highlight their absolute lowest sleep-mode current, which often corresponds to the current the system consumes when the real-time clock and

brownout detector are disabled. Some vendors go a step further and quote a shutdown-mode current that does not retain memory and requires a reset to wake up, which in general is not a practical mode. Therefore, because most applications require full RAM

and register retention, it is important to perform side-by-side comparisons using the standby/sleep-mode current with real-time clock and brownout disabled with RAM retention, standby/sleep-mode current with real-time clock disabled and brownout enabled, and standby/sleep-mode current with real-time clock and brownout enabled. You can then use the correct values when calculating the overall standby-mode power budget based on the duty cycle of the application.

#### **WAKE-UP ENERGY**

Systems that use sleep modes can waste a significant amount of power waking up the microcontroller and preparing it to acquire or process data. In some applications, a microcontroller can often use just as much energy when coming out of standby as when the device is fully processing data. Therefore, it is important to design a microcontroller to wake up and settle in a short time to minimize the amount of time it spends in an energy-wasting state. The microcontroller should be able to exit sleep mode from either an external

# **EFE SERIES**High Density Power Supplies

Large power requirements but limited on space?

No need to let fur fly, TDK-Lambda has a solution. The EFE300 delivers 300W in the industry standard 3 x 5" footprint, or 400W in the compact 3 x 6" EFE400.

Medical application? The fully featured EFE300M is rated at 300W (400W peak) and has medical safety certifications, including BF rated output isolation.

Don't pussy foot around, contact TDK-Lambda for an evaluation unit or check our website for distribution inventory.

http://us.tdk-lambda.com/lp/products/efe-series.htm

- ◆ 300 & 400W Output Power

- 12 to 48V Output

- ◆ 3 x 5" & 3 x 6" size

- Medical rating (EFE300M)

- Suitable for 1U Applications

- ◆ Three Year Warranty

- Open frame or enclosed with fan option

For more information on how TDK-Lambda can help you power your unique applications, visit our web site at

www.us.tdk-lambda.com/lp/ or call 1-800-LAMBDA-4

Figure 2 A low-dropout regulator can hold microcontroller power consumption constant across a wide supply-voltage range.